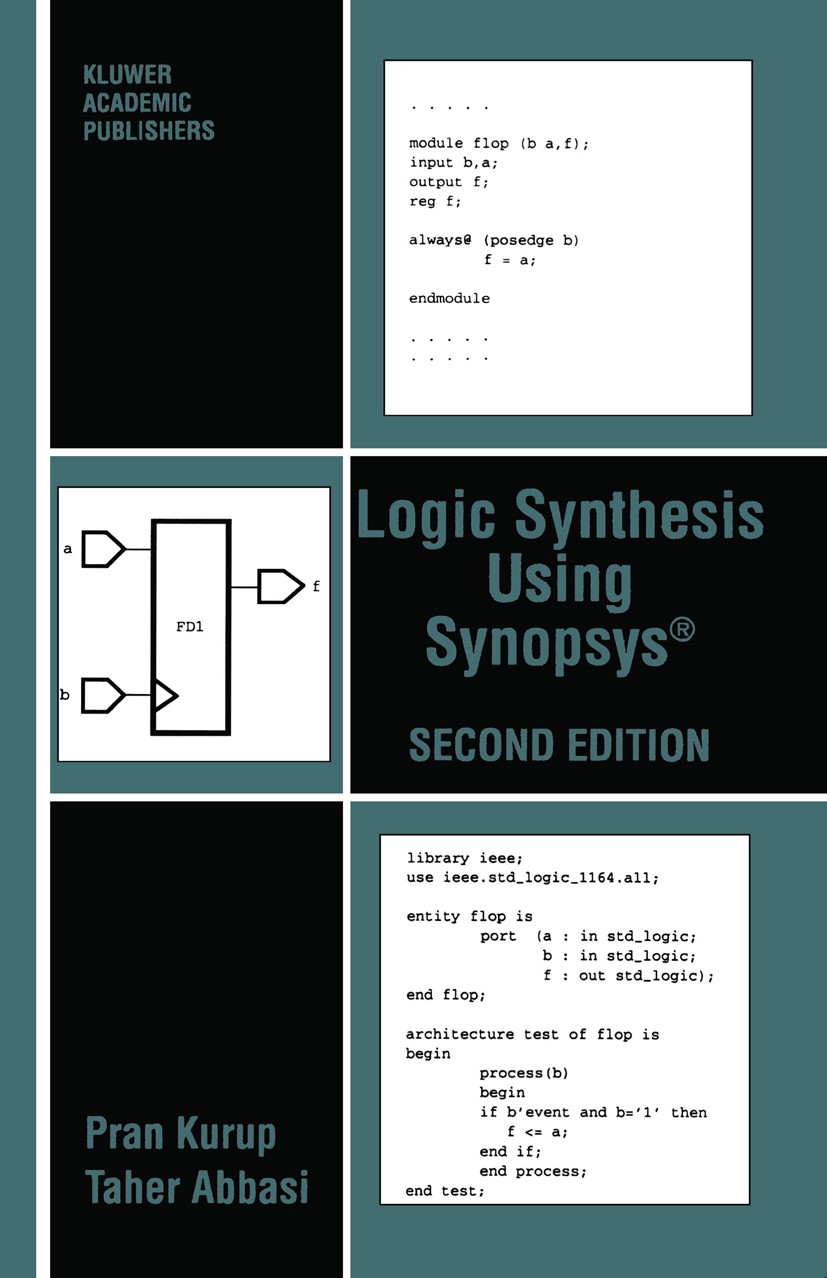

| 書目名稱 | Logic Synthesis Using Synopsys? | | 編輯 | Pran Kurup,Taher Abbasi | | 視頻video | http://file.papertrans.cn/588/587929/587929.mp4 | | 圖書封面 |  | | 描述 | .Logic Synthesis Using Synopsys.?., SecondEdition. is for anyone who hates reading manuals but would stilllike to learn logic synthesis as practised in the real world. Synopsys.Design Compiler., the leading synthesis tool in the EDAmarketplace, is the primary focus of the book. The contents of thisbook are specially organized to assist designers accustomed toschematic capture-based design to develop the required expertise toeffectively use the Synopsys .Design. .Compiler.. Over 100`Classic Scenarios‘ faced by designers when using the .DesignCompiler. have been captured, discussed and solutions provided.These scenarios are based on both personal experiences and actual userqueries. A general understanding of the problem-solving techniquesprovided should help the reader debug similar and more complicatedproblems. In addition, several examples and dc_shell scripts(.Design Compiler. scripts) have also been provided. ..Logic Synthesis Using Synopsys.?., Second Edition. is anupdated and revised version of the very successful first edition..The second edition covers several new and emerging areas, in additionto improvements in the presentation and contents in all chapters fromthe first edi | | 出版日期 | Book 1997Latest edition | | 關(guān)鍵詞 | ASIC; FPGA; Field Programmable Gate Array; Phase; RTL; VHDL; Verilog; computer-aided design (CAD); geometry; | | 版次 | 2 | | doi | https://doi.org/10.1007/978-1-4613-1455-4 | | isbn_softcover | 978-1-4612-8634-9 | | isbn_ebook | 978-1-4613-1455-4 | | copyright | Kluwer Academic Publishers 1997 |

The information of publication is updating

|

|

|Archiver|手機(jī)版|小黑屋|

派博傳思國(guó)際

( 京公網(wǎng)安備110108008328)

GMT+8, 2025-10-7 07:49

|Archiver|手機(jī)版|小黑屋|

派博傳思國(guó)際

( 京公網(wǎng)安備110108008328)

GMT+8, 2025-10-7 07:49